# 600E MX Series Drop-In GaN Control Board

Controller Plus Switch for Fast Prototyping

# XSYSTOR

PRODUCT FLYER August 2021

#### **General Description**

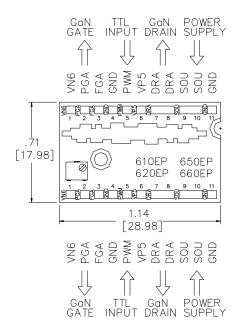

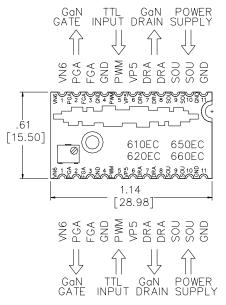

The 600E MX Series are general purpose and complete solutions to operate most GaN devices. The on-board Controller and Switch provide bias adjustment, power sequence, and protection. Demonstrating device performance is as easy as dropping them in on GaN eval boards, subassemblies, and test apparatus. The tiny modules can be mounted on either metal surfaces or on printed circuit boards. Identical connections at opposite sides of the module simplifies placement for fast-prototyping. Drop it, set it, and forget it.

#### **Features**

Controller Assembly:

- Single power supply. Reliable Power Sequencing from all supply scenarios

- Drain switching is controlled by TTL logic in Active-Low or Active-High

#### Drain Switch Assembly:

- Rated for 80V, Ultra-low Rds ON, Operation up to 150°C, with derated voltage and current

- Available in 8A or 16A CW operation with optimal heatsinking

#### Gate Bias Control:

On-board potentiometer included for fine gate bias adjustment

#### **Eval Board Configurations**

TYPE-EP typically mounts on metal surfaces, while TYPE-EC on printed circuit boards.

610EC, 620EC, 650EC, 660EC

### **Specification Snapshot**

| Parameter                                                                                                                                                                                                 | Min             | Max                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------|

| Supply (+) Voltage                                                                                                                                                                                        | +20 V           | +65 V                                                                 |

| Supply (-) Voltage, Optional                                                                                                                                                                              | -6 V            | 0 V                                                                   |

| Internal (-) Supply V, Gate Pinchoff                                                                                                                                                                      | -4.3 V          |                                                                       |

| Internal (-) Supply I                                                                                                                                                                                     | -30 mA          |                                                                       |

| Opt External Supply V & Pinchoff                                                                                                                                                                          | -6.0 V          |                                                                       |

| Optional External (-6V) Supply I                                                                                                                                                                          | -100 mA         |                                                                       |

| Gate Bias Voltage Range                                                                                                                                                                                   | -4.3V           | -0.5 V                                                                |

| TTL Voltage Logic High                                                                                                                                                                                    | +2.5 V          | +5.0 V                                                                |

| TTL Voltage Logic Low                                                                                                                                                                                     | 0 V             | +1.5 V                                                                |

| Avg Current from MOS peak rating                                                                                                                                                                          |                 | 30%                                                                   |

| MOS Rds ON                                                                                                                                                                                                | 0.02 Ω          | 0.05 Ω                                                                |

| Drain ON Prop Delay, loaded                                                                                                                                                                               |                 | 600 ns                                                                |

| Drain ON Rise Time, loaded                                                                                                                                                                                |                 | 300 ns                                                                |

| Drain OFF Prop Delay, loaded                                                                                                                                                                              |                 | 10 us                                                                 |

| Drain OFF Fall Time, loaded                                                                                                                                                                               |                 | 5 us                                                                  |

| Soldering Temp (10 sec)                                                                                                                                                                                   |                 | +260°C                                                                |

| Operating Temperature                                                                                                                                                                                     | -40°C           | +85°C                                                                 |

| Storage Temperature                                                                                                                                                                                       | -65°C           | +150°C                                                                |

| Avg Current from MOS peak rating MOS Rds ON Drain ON Prop Delay, loaded Drain ON Rise Time, loaded Drain OFF Prop Delay, loaded Drain OFF Fall Time, loaded Soldering Temp (10 sec) Operating Temperature | 0.02 Ω<br>-40°C | 30%<br>0.05 Ω<br>600 ns<br>300 ns<br>10 us<br>5 us<br>+260°C<br>+85°C |

Propagation Delay is measured from 90% of TTL to 10% of Drain Voltage with device load . Rise/Fall Times are measured at 10% and 90% of signal. Both measurements are summed for total time.

## **Ordering Information**

| Content<br>Type | Mount<br>Type | Shut-<br>down<br>Preset | TTL<br>Enable | Misc<br>Type |    |

|-----------------|---------------|-------------------------|---------------|--------------|----|

| 610             | EP            | 2R6                     | AL            | 20           | MX |

| 620             | EC            | 2R0                     | AH            | 50           |    |

| 650             |               | 1R4                     |               |              |    |

| 660             |               | 0R8                     |               |              |    |

Example: 620EP2R0AL20MX

610\_100X Controller & 8A Avg (16A Peak) Switch

620\_200X Controller & 8A Avg (16A Peak) Switch

650\_100X Controller & 16A Avg (36A Peak) Switch

660\_200X Controller & 16A Avg (36A Peak) Switch

6FP\_Mounts on Metal. Pads on top, Ground at bottom

EC\_Mounts on PCB. Castellated ports for solder reflow

2R6...0R8\_Gate Threshold Shutdown Presets at -2.6V,

-2.0V,-1.4V,-0.8V. Has provisions for fine adjustment

using one resistor. Refer to XAN-2 application note

AL\_Active-Low (0V) TTL for Gate/Drain Voltage ON

AH\_Active-High (<5V) TTL for Gate/Drain Voltage ON

20\_Supply range of +20V to +36V. General purpose

50\_Supply range of +36V to +65V. General purpose

### I/O Pin Descriptions

| 610<br>620 | 630<br>640 | LABEL                                                                                                                                                              | DESCRIPTION                                                                 |  |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| PIN        | PIN        |                                                                                                                                                                    |                                                                             |  |

| 1          |            | VN6                                                                                                                                                                | Optional Neg Voltage Input (-6V min) for Gate<br>Current Boost. Leave Open. |  |

| 2          | 1          | PGA Neg Pulsed Voltage Output to Transistor Gate                                                                                                                   |                                                                             |  |

| 3          |            | FGA Neg Fixed Voltage Output to Transistor Gate                                                                                                                    |                                                                             |  |

| 4          | 4          | GND                                                                                                                                                                | Ground                                                                      |  |

| 5          | 2          | PWM                                                                                                                                                                | TTL/PWM Signal Input to Switch Transistor.                                  |  |

| 6          |            | VP5                                                                                                                                                                | Optional Positive Voltage Input (+5V max). Leave Open.                      |  |

| 7,8        | 7,8,9      | DRA High Voltage Output to Transistor Drain. Avoid excess wires or lines to minimize inductive parasitic. Max capacitive load is 500pF for optimum switching speed |                                                                             |  |

| 9,10       | 10,11      | High Voltage Power Supply Input. Connect high value storage capacitors here.                                                                                       |                                                                             |  |

| 11         |            | GND                                                                                                                                                                | Ground                                                                      |  |

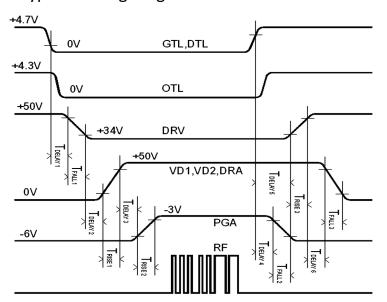

### **Typical Timing Diagrams**

Refer to Application Note XAN-2 for further details.

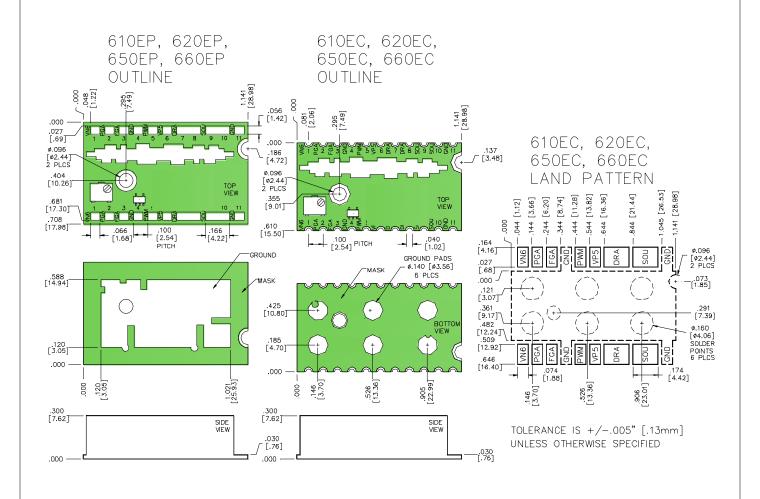

#### **Outline & Land Pattern**